?一、 实验目的熟悉判零线路;掌握进位寄存器单元的工作原理运用;掌握带进位控制的算术逻辑运算器的组成和硬件电路。?二、 实验内容完成算术逻辑单元带进位的位加法运算;完成带进位移位实验。?三、 实验详情实验1:算术逻辑单元带进位位的加法运算实验

● 把alu-in(8芯的盒型插座)与右板上的二进制开关单元中j01插座相连(对应二进制开关h16~h23),把alu-out(8芯的盒型插座)与数据总线上的dj2相连。

● 把D1CK、D2CK、CCK用连线连到脉冲单元的PLS1上,把EDR1、EDR2、ALU-O、S0、S1、S2、S3、CN、M接入二进制拨动开关(请按下表接线)。

控制信号

接入开关位号

D1CK

PLS1 孔

D2CK

PLS1 孔

CCK

PLS1 孔

EDR1

H8 孔

EDR2

H7 孔

ALU-O

H6 孔

CN

H5 孔

M

H4 孔

S3

H3 孔

S2

H2 孔

S1

H1 孔

S0

H0 孔

接线图示:

● 按启停单元中停止按钮,实验平台停机并且把进位寄存器CY清零(CY灯灭)。在本实验中使用算术逻辑单元作为进位发生器,按运行键,实验即进入运行状态。

● 二进制开关H16~H23作为数据输入,置65H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

0

1

1

0

0

1

0

1

65H

置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

0

1

0

1

0

1

0

0

1

● 按脉冲单元中的PLS1脉冲按键,在D1CK上产生一个上升沿,把65H打入DR2数据锁存器,通过逻辑笔或示波器来测量确定DR2寄存器(74LS374)的输出端,检验数据是否进入DR2中。置S3、S2、S1、S0、M为11101时,总线指示灯显示DRl中的数,而置成10010时总线指示灯显示DR2中的数。

● 二进制开关H16~H23作为数据输入,置A7H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

1

0

1

0

0

1

1

1

A7H

置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

1

0

1

1

0

1

0

0

1

● 按脉冲单元中的PLS1脉冲按键,在D2CK上产生一个上升沿,把A7H打入DR2数据锁存器。

● 再置各控制信号如下:

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

1

1

0

1

0

1

0

0

1

● 按脉冲单元中的PLS1脉冲按键,在CCK上产生一个上升沿,把74LS181的进位打入进位寄存器中,在有进位的情况下,CY指示灯亮,并且ALU-O为0,把计算结果输出到数据总线。

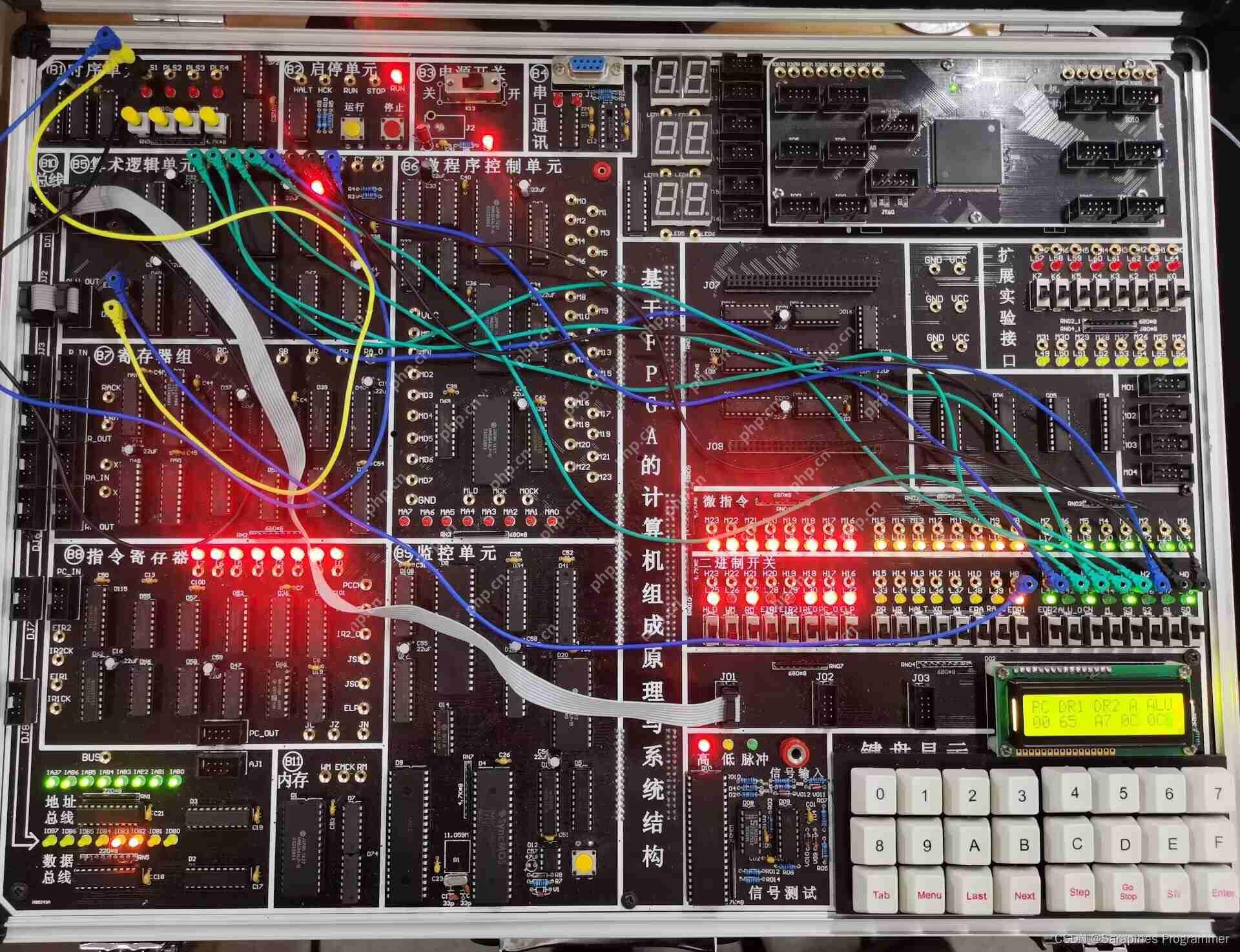

● 经过74LS181的计算将产生进位,即Cn+4输出0,当把计算结果输出到总线时,数据总线指示灯IDB0~IDB7将显示结果0CH。

● 按启停单元中停止按钮,实验平台停机时把进位寄存器CY清零(CY灯灭)。在本实验中使用通用寄存器作为进位发生器,按运行键,实验即进入运行状态。

把RA-IN(8芯的盒型插座)与右板上的二进制开关单元中J01相连(对应二进制开关H16~H23),把RA-OUT(8芯的盒型插座)与数据总线上的DJ6相连。

● 把CCK、RACK连到脉冲单元的PLS1,把ERA、X0、X1、RA-O、M接入二进制拨动开关。(请按下表接线)。

信号定义

接入开关位号

CCK

PLS1 孔

RACK

PLS1 孔

X0

H12 孔

X1

H11 孔

ERA

H10 孔

RA-O

H9 孔

M

H4 孔

接线图示:

● 二进制开关H16~H23作为数据输入,置81H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

1

0

0

0

0

0

0

1

81H

置各控制信号如下:

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

1

1

0

0

0

● 按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,把81H打入通用寄存器内。

● 此时数据总线上的指示灯IDB0~IDB7 应该显示为81H。由于通用寄存器内容不为0,所以ZD(LED)灯灭。

置各控制信号如下:

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

0

1

0

0

0

● 按脉冲单元中的PLS1脉冲按键,在RACK上产生一个上升沿,使通用寄存器中的值左移。因进位寄存器CY的初始值为0,在RACK脉冲作用下将CY打入通用寄存器的最低位Q0。同时在CCK脉冲作用下把通用寄存器的最高位Q7(为1)打入进位寄存器CY,使CY显示灯亮,这样就实现了带进位的左移功能。

● 同样置各控制信号如下,并且按脉冲单元中的PLS1脉冲按键,可实现带进位的右移功能。

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

1

0

0

0

0

把M作为是否带进位的选择,M=0 带进位移位,M=1不带进位移位。控制型号X0、X1、M的功能状态如下:

功能状态表

X1

X0

M

功能

移位操作

0

1

1

循环右移

Q7->Q6->Q5->Q4->Q3->Q2->Q1->Q0

0

1

0

带进位循环右移

CY->Q7->Q6->Q5->Q4->Q3->Q2->Q1->Q0

1

0

1

循环左移

Q7

1

0

0

带进位循环左移

CY

(1)step1:把ALU-IN、ALU-OUT分别与二进制开关单元JO1和总线DJ2相连,并把D1CK、D2CK、CCK使用连接线接到脉冲单元的PLS1上,具体接线如下表。

控制信号

接入开关位号

D1CK

PLS1

孔

D2CK

PLS1

孔

CCK

PLS1

孔

EDR1

H8

孔

EDR2

H7

孔

ALU-O

H6

孔

CN

H5

孔

M

H4

孔

S3

H3

孔

S2

H2

孔

S1

H1

孔

S0

H0

孔

(2)step2:按停止按钮,机箱停机将CY清零,再按运行键。二进制开关H16至H23作为数据输入,置65H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

0

1

1

0

0

1

0

1

65H

置各控制信号如下表.

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

0

1

0

1

0

1

0

0

1

(3)step3:按下机箱的PLS1脉冲按键,在D1CK产生上升沿,把65H打入DR1锁存器中。

二进制开关H16至H23作为数据输入,置A7H(对应开关如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

1

0

1

0

0

1

1

1

A7H

置各控制信号如下表.

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

1

0

1

1

0

1

0

0

1

按下机箱的PLS1脉冲按键,在D1CK产生上升沿,把A7H成功打入DR2锁存器中。

置各控制信号如下表.

H8

H7

H6

H5

H4

H3

H2

H1

H0

EDR1

EDR2

ALU-O

CN

M

S3

S2

S1

S0

1

1

0

1

0

1

0

0

1

按下机箱的PLS1脉冲按键,在D1CK产生上升沿,总线指示灯IDB0至IDB7显示结果0CH。

(1)step1:将CY清零,重新按运行键使机箱处于运行状态。RA-IN、RA-OUT分别与二进制开关单元JO1和总线DJ6相连,并把RACK、CCK使用连接线接到脉冲单元的PLS1上,具体接线如下表。

控制信号

接入开关位号

CCK

PLS1

孔

RACK

PLS1

孔

X0

H12

孔

X1

H11

孔

ERA

H10

孔

RA-O

H9

孔

M

H4

孔

(2)step2:二进制开关H16至H23作为数据输入,置81H(如下表)。

H23

H22

H21

H20

H19

H18

H17

H16

数据总线值

D7

D6

D5

D4

D3

D2

D1

D0

8位数据

1

0

0

0

0

0

0

1

81H

置各控制信号如下表.

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

0

1

0

0

0

(3)step3:按下机箱的PLS1脉冲按键,在D1CK产生上升沿,实现带进位的左移功能。

然后置各控制信号如下表.

H12

H11

H10

H9

H4

X0

X1

ERA

RA-O

M

1

0

0

0

0

按下机箱的PLS1脉冲按键,在D1CK产生上升沿,实现带进位的右移功能。

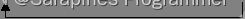

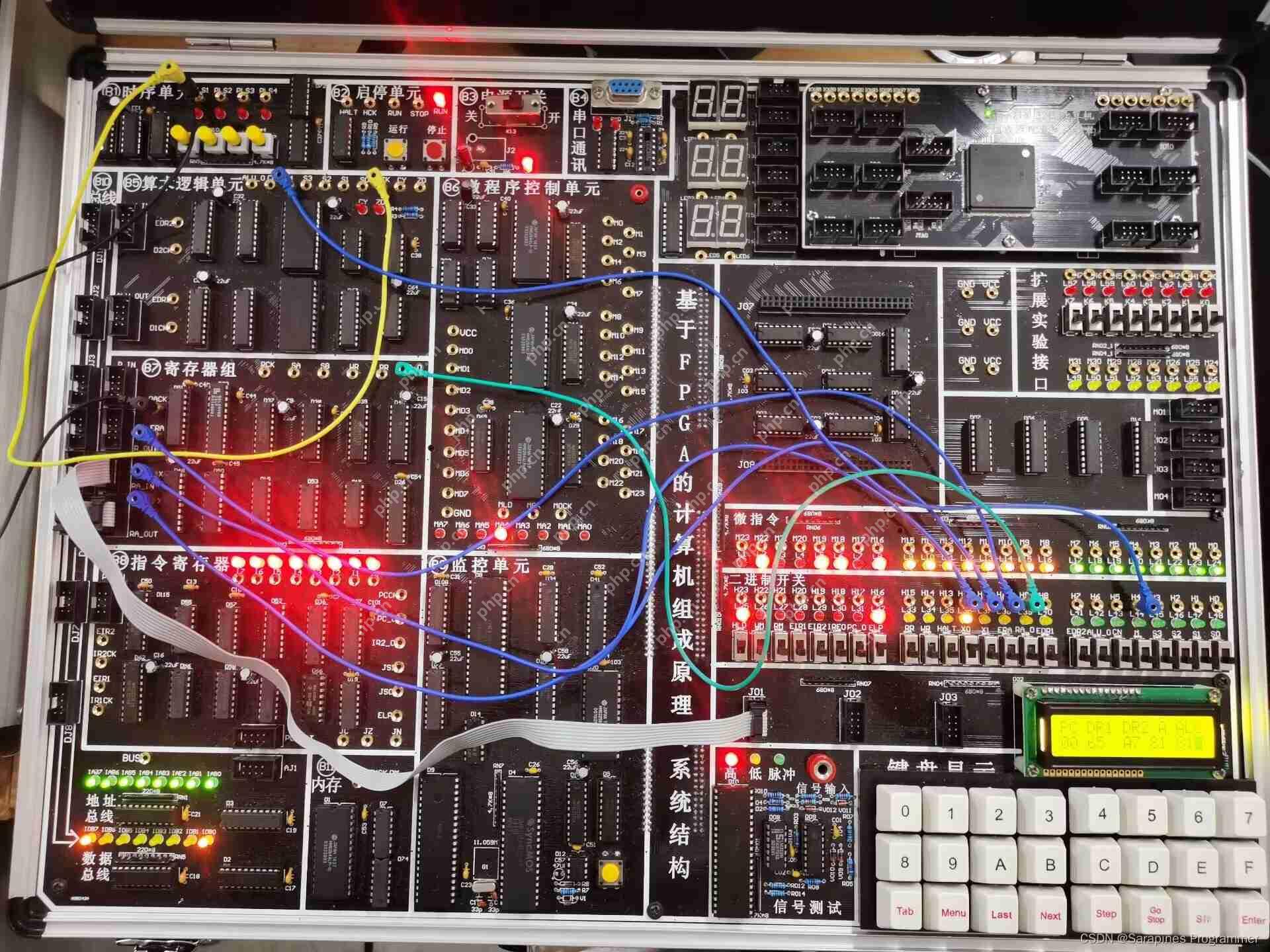

实验1 算术逻辑单元带进位的位加法运算

实验1平台

实验1结果

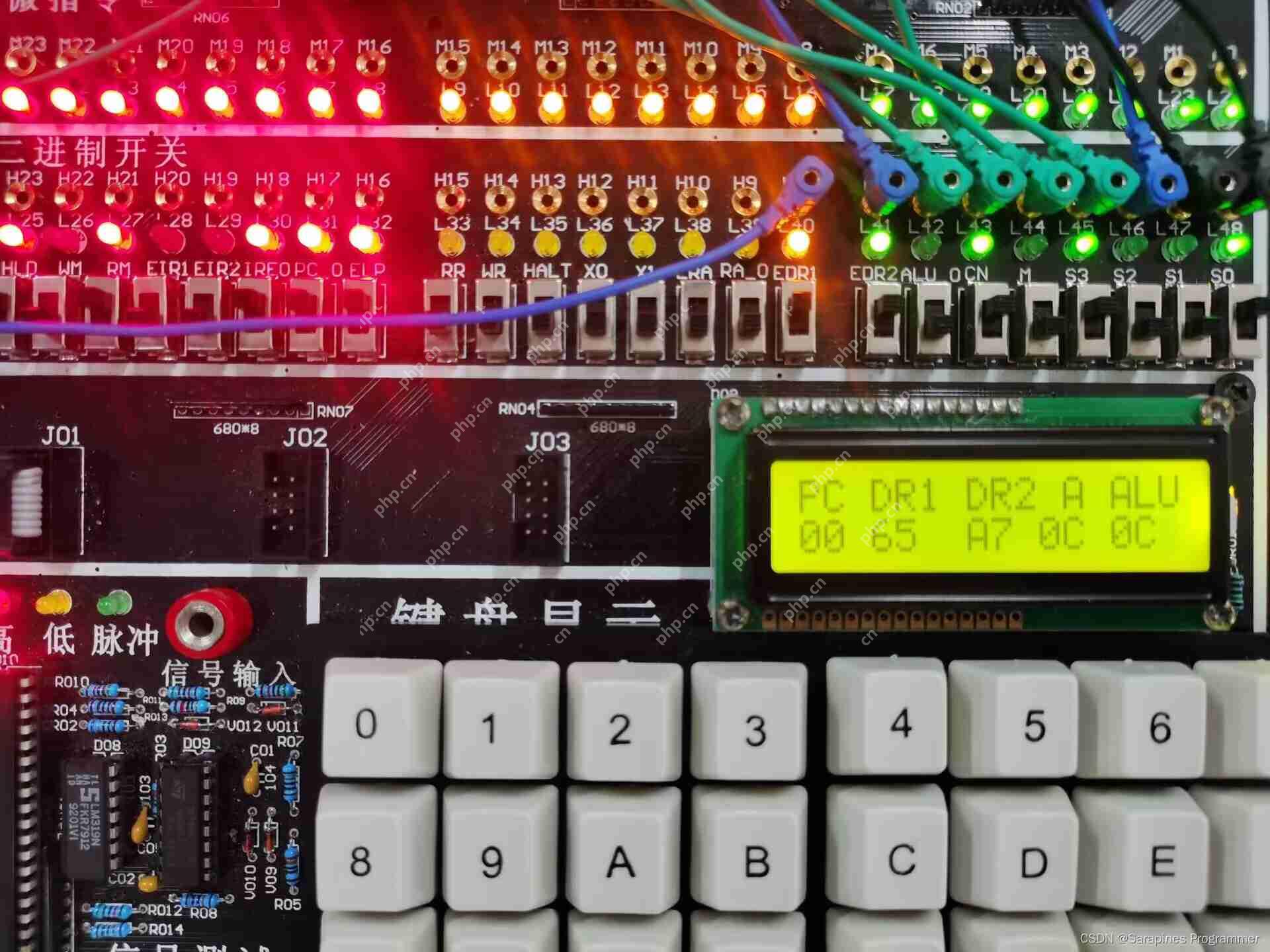

实验2 带进位移位实验

实验2第一阶段平台

实验2第一阶段平台

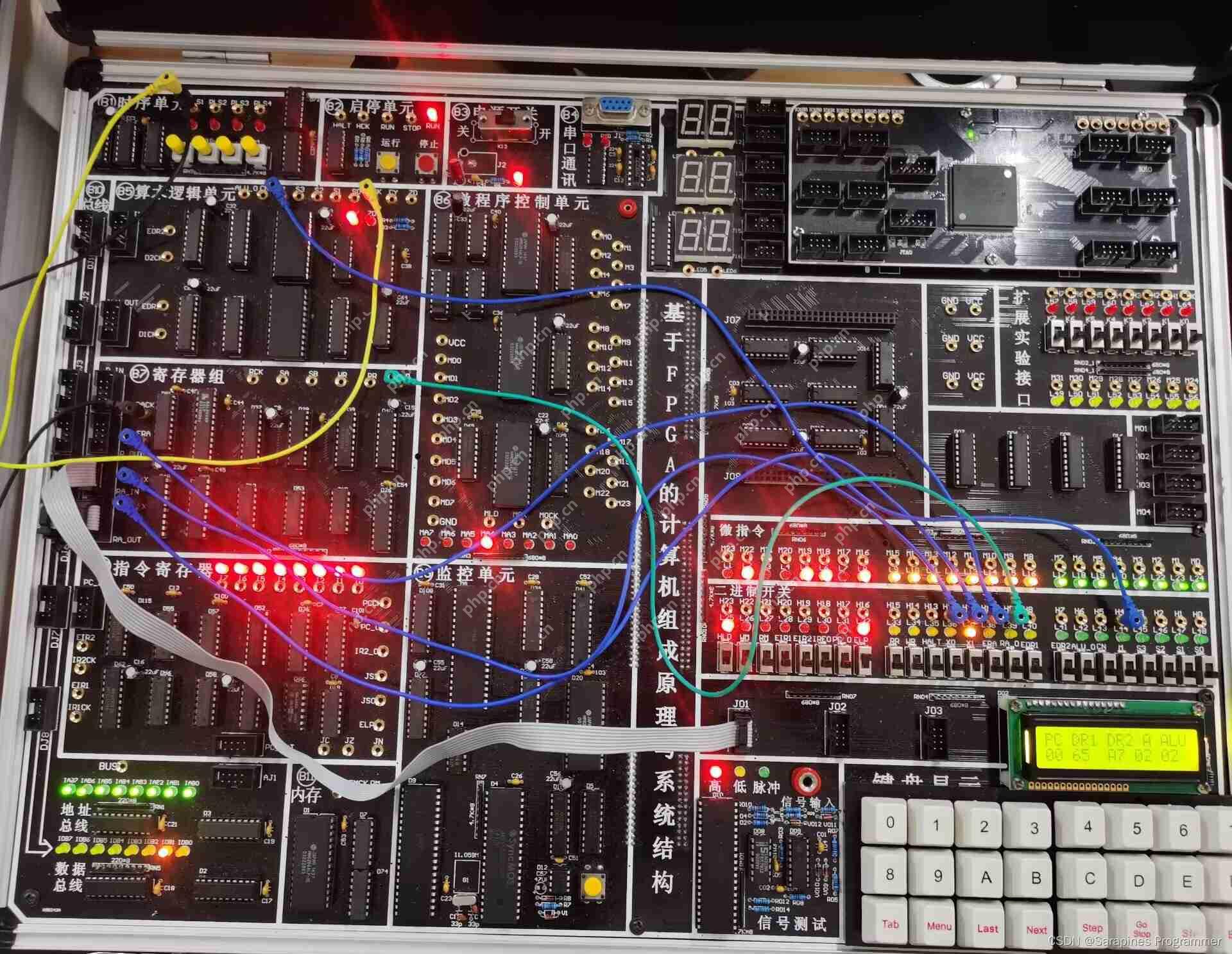

实验2第二阶段平台

实验2第二阶段结果

通过对实验操作以及结果分析,我熟悉了判零线路;掌握了在控制部分通过启停按键和运行按键以清零CY寄存器,并控制实验是否产生进位、左移或右移;熟悉了带进位控制的算术逻辑运算器的组成、硬件电路以及利用进位寄存器来实现带进位的左移、右移。

?总结计算机组成原理领域就像一片广袤而未被完全探索的技术海洋,邀请你勇敢踏足数字世界和计算机组成原理的神秘领域。这是一场结合创造力和技术挑战的学习之旅,从基础概念到硬件实现,逐步揭示更深层次的计算机结构、指令集架构和系统设计的奥秘。渴望挑战计算机组成原理的学习路径和掌握计算机硬件的技能?不妨点击下方链接,一同探讨更多数字技术的奇迹吧。