在simulink建模过程中,clock模块是一项基础而关键的组件,它为整个仿真系统提供统一的时间参考,是实现各类时间依赖行为的核心支撑。

时间戳生成与状态捕获

Clock模块可实时输出当前仿真时刻,具备高精度的时间戳生成能力。将其输出信号接入数据存储模块(如To Workspace、To File)或与其他状态变量并行记录,即可在仿真运行中同步保存各时间节点下的系统响应。例如,在电机控制系统建模中,结合Clock模块与Scope或Logging工具,可完整追踪转速、电流等关键参数随时间变化的全过程,为性能评估与故障诊断提供高质量时序数据。

定时触发与逻辑切换

借助Clock模块输出的时间信号,可灵活构建基于时间的条件判断机制。典型应用包括:在t=5s时启动PID控制器、在t=10s后关闭某执行机构、或按时间段切换不同控制策略。通过将其输出接入Relational Operator(如>=、==)及Switch、Enabled Subsystem等模块,即可实现毫秒级精度的时序逻辑控制,显著增强模型的行为可控性与场景适配性。

循环任务调度

Clock模块是构建周期性行为的理想起点。例如,设定每0.1秒采集一次传感器数据、每1秒更新一次滤波器参数、或每5秒执行一次状态重置操作。只需将Clock输出与Modulo(取模)模块或自定义逻辑单元配合使用,即可生成稳定可靠的周期脉冲信号,驱动Function-Call Subsystem或Triggered Subsystem完成重复性任务,保障系统运行节奏的一致性与可预测性。

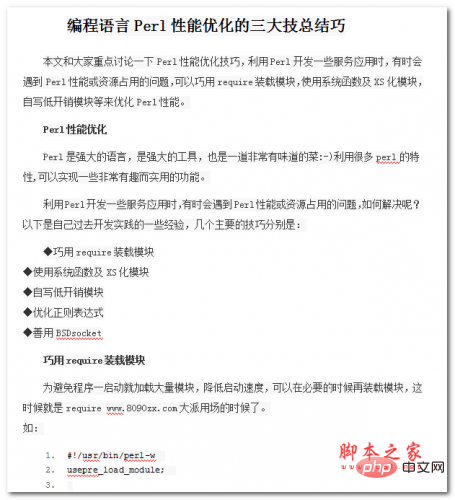

本文和大家重点讨论一下Perl性能优化技巧,利用Perl开发一些服务应用时,有时会遇到Perl性能或资源占用的问题,可以巧用require装载模块,使用系统函数及XS化模块,自写低开销模块等来优化Perl性能。 Perl是强大的语言,是强大的工具,也是一道非常有味道的菜:-)利用很多perl的特性,可以实现一些非常有趣而实用的功能。希望本文档会给有需要的朋友带来帮助;感兴趣的朋友可以过来看看

外部实时时钟对齐

在硬件在环(HIL)、数字孪生或联合仿真等工程实践中,常需使Simulink模型时间与真实物理时钟保持同步。通过配置Simulation Time设置、引入External Mode或借助S-Function与主机系统时钟交互,Clock模块可作为时间基准参与对外部时间源的校准与跟踪,从而提升仿真结果在真实环境中的可信度与实用性。

时间维度可视化分析

将Clock模块输出直接连接至Scope、Dashboard Chart或XY Graph等可视化模块,能够清晰呈现仿真时间轴的推进过程,并支持与其他信号叠加显示,直观反映控制动作、事件触发及系统响应在时间域上的对应关系。这种时序可视化手段对于排查逻辑时序错误、验证采样周期合理性以及优化仿真步长设置具有重要辅助价值。

综上所述,深入理解并高效运用Simulink中的Clock模块,不仅有助于构建逻辑严谨、时序明确的动态系统模型,更能显著提升建模效率、仿真精度与工程落地能力,是掌握高级建模仿真技术不可或缺的重要环节。